CONECTORES DA INTERFACE DIGITAL, DA PLACA FPGA, DO MICROPROCESSADOR ARM E DAS PLACAS DE SENSORES

CONECTORES DA INTERFACE DIGITAL

Na Fig.1 observam-se as fichas macho de terminação dos cabos planos, com 16 e 14 condutores, para transportar os sinais da interface digital do SUBA para uma 'breadboard'.

Todos os sinais lógicos da placa digital são activos a "1" (5 V). As setas indicam o sentido de entrada / saída dos sinais. Os sinais lógicos de saída são gerados por circuitos HCMOS ou HCTMOS e podem alimentar várias carga CMOS (ver especificações para cargas "TTL low Power"), pelo que pode ser necessário usar um andar tampão (Buffer), se estes sinais atacarem várias entradas lógicas.

Os 2 cabos planos estão terminados com conectores que têm uma disposição de contactos do tipo macho, semelhantes aos pinos de um circuito integrado normal, mas a numeração dos pinos é feita de modo diferente, pois aqui esta numeração indica a posição de cada condutor dentro do cabo plano. No entanto, indica-se também a numeração clássica seguida para os pinos de circuito integrado.

Nos 2 conectores estão disponíveis vários portos com tensão de alimentação contínua de 5 V, estabilizada, e várias massas ( 0 V).

O sinal lógico INICIO1 vai momentaneamente (cerca de 1 ms) a "1" sempre que se liga o interruptor de alimentação do SUBA ou se carrega momentaneamente nos interruptores dos pára-choques, regressando depois a "0". O sinal lógico INICIO2 vai a "1" sempre que se mantém pressionado o interruptor dos pára-choques e depois de largado mantém-se ainda a "1" durante cerca de 1 ms.

Fig.1 - Fichas de terminação dos conectores nas placas de 'breadboard'

|

FARÓIS/VISOR IN na Ficha IDC |

MOTOR IN/CLOCKOUT/INT na Ficha IDC |

| 1- +5V - Saída da tensão de 5 V contínua | 1- FWD - Entrada lógica para activar motor de tracção para a frente |

| 2- PD - Entrada lógica para activar o ponto decimal do visor do tejadilho | 2- +5V - Saída da tensão de 5 V contínua |

| 3- A - Entrada lógica hexadecimal do dígito do visor do tejadilho | 3- BWD - Entrada lógica para activar motor de tracção para trás |

| 4- B - Entrada lógica hexadecimal do dígito do visor do tejadilho | 4- F1- Sinal proveniente do selector de frequências de relógio |

| 5- C - Entrada lógica hexadecimal do dígito do visor do tejadilho | 5- RIGHT - Entrada lógica para accionar motor de direcção para a direita |

| 6- D - Entrada lógica hexadecimal do dígito do visor do tejadilho | 6- F2- Sinal proveniente do selector de frequências de relógio |

| 7- LE- Entrada lógica que activa visor do tejadilho | 7- LEFT - Entrada lógica para accionar motor de direcção para a esquerda |

| 8- OV- Saída da massa (sinal e alimentação de 5 V) | 8- F3- Sinal proveniente do selector de frequências de relógio |

| 9- VBAT- Saída da tensão da bateria do SUBA (~+10 V) | 9- F5- Sinal proveniente do selector de frequências de relógio |

| 10- FE- Entrada lógica para activar farol de emergência do tejadilho | 10- F4- Sinal proveniente do selector de frequências de relógio |

| 11- Fm- Entrada lógica para activar farol de médios | 11- INICIO1- Saída lógica resultante do botão de pressão do pára-choques |

| 12- FM- Entrada lógica para activar farol de máximos | 12- INICIO2- Saída lógica resultante do botão de pressão do pára-choques |

| 13- PD- Entrada lógica para activar luzes de pisca direito | 13- OV- Saída da massa (sinal e alimentação de 5 V) |

| 14- PE- Entrada lógica para activar luzes de pisca esquerdo | 14- ÁUDIO- Entrada de áudio para o amplificador de potência. |

| 15- OV- Saída da massa (sinal e alimentação de 5 V) | |

| 16- Fstp- Entrada lógica para activar luzes de travão |

Tabela 1- Sinais presentes nas fichas de terminação dos conectores.

CONECTORES DA PLACA DO ARM

Na Fig.2 observam-se as fichas macho de terminação do cabos plano, com 48 condutores, para transportar os sinais da interface digital do microprocessador ARM para uma placa tipo'breadboard'.

Fig.2 - Fichas de terminação do processador ARM nas placas de 'breadboard'

CONECTORES DA PLACA FPGA "COREWORKS"

Na Fig.3 observam-se as fichas macho de terminação do cabos plano, com 24 condutores, para transportar os sinais da interface digital da placa FPGA para uma placa tipo'breadboard'.

Fig.3- Fichas de terminação da placa FPGA nas placas de 'breadboard'

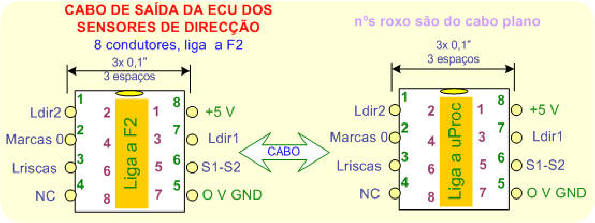

CONECTORES DA PLACA SENSORES DE DIRECÇÃO

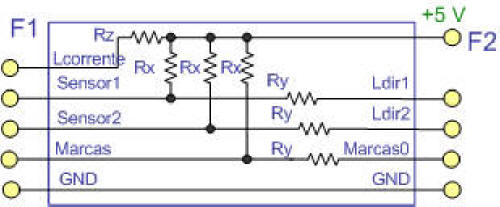

Na Fig. 4 observam-se as fichas macho de terminação do cabos plano, com 8 condutores, para transportar os sinais do sensor de direcção do SUBA para a ECU dos sensores de direcção onde são gerados os sinais lógicos correspondentes á informação analógica adquirida pelo sensor de direcção. A ECU dos sensores da direcção, Fig. 5, tem um porto F1 de ligação ao sensor de direcção (onde se inclui também a excitação de LEDs indicadores de direcção colocados no pára-choques), e tem o porto F2 onde se obtêm os sinais lógicos de saída. O porto F2 pode ser ligado a um microprocessador ou a um processador digital através do cabo representado na Fig. 7.

Fig.4- Cabo do sensor de direcção.

Fig.5- ECU dos sensores de direcção com os portos F1 e F2.

Nalguns casos a ECU dos sensores de direcção pode ser muito simplesmente realizada por resistências Rx de 68 kW que ligam os portos de entrada de F1, Marcas, Sensor 1 e Sensor 2, à tensão VCC de + 5 V. Os sinais de saída, Marcas0, Ldir1 e Ldir2, serão, neste caso, obtidos a partir dos próprios sinais de entrada através de resistências limitadoras Ry com o valor de 10 kW. A resistência Rz, de 330 W, destina-se a fornecer corrente aos acopladores ópticos instalados no sensor de direcção.

Fig.6- ECU dos sensores de direcção simplificada para ligação a microprocessador

com elevada impedância de entrada nos portos (> 100 kW).

Fig. 7- Cabo de saída da ECU dos sensores de direcção.

|

F1 - CONECTOR 1 (Entrada da ECU da direcção) |

F2 - CONECTOR 2 (Saída da ECU da direcção) |

| 1- Ldir2 - Saída de corrente para LED 2 do para choques | 1- Ldir2 - Saída lógica correspondente ao foto transístor 2 |

| 2- Lcorrente - Saída de corrente para 3 LEDS IV dos sensores | 2- Marcas 0 - Saída lógica do sensor de marcas (código de barras) |

| 3- Sensor 2 - Entrada de corrente gerada no foto transístor 2 | 3- Lriscas - Saída lógica com riscas dos sensores 1 e 2 |

| 4- GND - Ligação da massa dos sensores de direcção | 4- NC- não ligado |

| 5- Sensor 1 - Entrada de corrente gerada no foto transístor 1 | 5- GND- Entrada 0V da tensão de alimentação |

| 6- Marcas - Entrada de corrente gerada no foto transístor 3 | 6- Dif- Sinal analógico diferença dos sinais gerados nos sensores 1 e 2 |

| 7- Ldir 1- Saída com corrente para LED 1 para choques | 7- Ldir 1 - Saída lógica correspondente ao foto transístor 1 |

| 8- Riscas/Marcas - Saída com corrente para LED para choques Marcas/Riscas | 8- +VCC - Entrada da tensão de alimentação +5V. |

Tabela 2- Sinais presentes nos conectores da ECU dos sensores de direcção.

CONECTORES DOS SENSORES DO DIFERENCIAL MECÂNICO TRASEIRO

Na Fig.5 observa-se a placa de união das ligações provenientes dos cabos planos com 5 condutores, Esq. e Dir., provenientes dos sensores de movimento das rodas esquerda e direita, respectivamente. A placa de união está dotada de uma ficha IDC macho onde liga um cabo plano com 8 condutores e que termina numa ficha de "breadboard" com 8 condutores, ver Fig. 6.

Fig.5 - Placa união dos sensores do diferencial traseiro.

|

CONECTOR UNIÃO DIFERENCIAL Ficha IDC |

CONECTORES Esq. Dir. das Rodas |

| 1- NC | 1- +VCC - Entrada da tensão de alimentação +5V. |

| 2- GND - Entrada 0V da tensão de alimentação | 2- "Enable" - Entrada lógica "1" activa sensores das rodas |

| 3- NC | 3- D2- Saída lógica 2 da roda correspondente |

| 4- NC | 4- GND - Entrada 0V da tensão de alimentação |

| 5- D1E - Saída lógica 2 da roda esquerda | 5- D1- Saída lógica 1 da roda correspondente |

| 6- D1D - Saída lógica1 da roda direita | |

| 7- D2E- Saída lógica 2 da roda esquerda | |

| 8- D2D- Saída lógica 2 da roda direita | |

| 9- +VCC - Entrada da tensão de alimentação +5V. | |

| 8- "Enable" - Entrada lógica "1" activa sensores das rodas |

Tabela 3- Sinais presentes nos conectores da placa união dos sensores das rodas traseiras (diferencial).

Fig.6- Fichas de terminação dos sensores de movimento das rodas traseiras.